## Imperial College London

Department of Electrical and Electronic Engineering

Final Year Project Report 2022

Project Title: Combinational Logic Visualisation for ISSIE

Student: Aditya Deshpande

CID: **01504794**

Course: EIE4

Project Supervisor: Dr Thomas J. W. Clarke

Second Marker: Mr S. Baig

## Final Report Plagiarism Statement

I affirm that I have submitted, or will submit, an electronic copy of my final year project report to the provided EEE link.

I affirm that I have submitted, or will submit, an identical electronic copy of my final year project to the provided Blackboard module for Plagiarism checking.

I affirm that I have provided explicit references for all the material in my Final Report that is not authored by me, but is represented as my own work.

## Acknowledgments

First and foremost, I would like to thank my project supervisor, Dr Thomas Clarke, for his invaluable guidance and support throughout the duration of the Final Year Project, as well as introducing me to the F# programming language in my third year at Imperial College London – something which led me to choose this project.

I am also deeply grateful to my parents. They have always inspired me to reach for new heights, while always supporting me so that I can do so without fear of falling.

Finally, I would also like extend my thanks to all previous Issie developers for contributing to this wonderful application and making it a solid platform for me to build on top of.

#### Abstract

Issie (Interactive Schematic Simulator with Integrated Editor) is an education-focused digital electronics design platform used by students at Imperial College London, featuring an intuitive user-friendly UI and capable logic simulator. One of the many challenges a student may face when learning to design digital logic is conceptualising relationships between inputs and outputs in combinational logic, and how they relate to design specifications. This project extends the existing Issie application, exploring novel ways to communicate these logic relationships to the user. This is primarily achieved through the implementation of interactive automatic schematic-derived truth tables, which can be manipulated, reduced, and filtered to describe combinational logic relationships in numeric and algebraic forms. This involved the definition of an alternative formal language to Boolean algebra for representing combinational logic.

Additionally, this project has also made changes to the top-level UI of the application to make the user experience more consistent and conducive to learning. The extended functionality delivered by the project is effective and performant; this has been confirmed through a user experience survey. The novel visualisation methods have been tested on circuits designed by EE students at Imperial College London. Large digital logic circuits, such as the Arithmetic Logic Unit of an 8-bit ARM CPU, can be condensed from a schematic containing billions of possible input combinations to a short algebraic truth table describing a few dozen cases.

# Contents

| 1        | Intr | oduction                                                |

|----------|------|---------------------------------------------------------|

|          | 1.1  | Project Motivation                                      |

|          | 1.2  | Project Definition                                      |

|          |      | 1.2.1 Core Principles of Issie                          |

|          |      |                                                         |

| <b>2</b> |      | kground                                                 |

|          | 2.1  | Pedagogical Considerations                              |

|          |      | 2.1.1 Memory Models                                     |

|          |      | 2.1.2 Educating Engineers                               |

|          |      | · · · · · · · · · · · · · · · · · · ·                   |

|          | 2.2  | Combinational Logic                                     |

|          |      | 2.2.1 Visualising Logic with Boolean Algebra            |

|          |      | 2.2.2 Visualising Logic with Schematic Diagrams         |

|          | 2.3  | Truth Tables                                            |

|          |      | 2.3.1 Reduction using Don't Cares                       |

|          |      | 2.3.2 Algebraic Truth Tables                            |

|          | 2.4  | An Overview of Issie's Technology Stack                 |

|          |      | 2.4.1 Programming Language                              |

|          |      | 2.4.2 Ecosystem                                         |

|          |      | 2.4.3 User Interface and Rendering                      |

|          |      | 2.4.4 Overview                                          |

|          | 2.5  | Issie's UI                                              |

|          |      | 2.5.1 Overview and Evaluation                           |

|          |      | 2.5.2 Considerations when adding new features           |

|          | 2.6  | Combinational Logic Simulation in Issie                 |

|          | 2.7  | Effects of Application Performance on Users             |

|          | 2.8  | Agile Software Development                              |

|          |      |                                                         |

| 3        | Pro  | ject Requirements                                       |

|          | 3.1  | Requirements for Combinational Logic Visualisation      |

|          | 3.2  | Software/Documentation Quality Requirements             |

|          |      |                                                         |

| 4        | Ana  | llysis and Design 21                                    |

|          | 4.1  | Approach towards Software Development                   |

|          | 4.2  | Technology Stack                                        |

|          | 4.3  | Top Level UI Changes                                    |

|          | 4.4  | Generating Numeric Truth Tables                         |

|          |      | 4.4.1 Decision to re-use Step Simulation Code           |

|          |      | 4.4.2 Evolution of the Input Space Generation Algorithm |

|          | 4.5  | Generating Truth Tables for a partial selections        |

|          | 4.6  | Filtering with Constraints                              |

|          |      | 4.6.1 Constraint Validation Rules                       |

|          | 4.7  | Hiding Output Columns                                   |

|          | 4.8  | Graphical Manipulation of Truth Tables                  |

|          | 4.9  | Don't Care Reduction                                    |

|          | 4.10 | Algebraic Truth Tables                                  |

|   | 4.11 | 4.10.1 Designing the System for Algebra                    |            |

|---|------|------------------------------------------------------------|------------|

| 5 | Imp  | plementation 3                                             | <b>2</b>   |

| • | 5.1  | Overview of Data Types                                     |            |

|   | 0.1  | 5.1.1 Types for Representing Truth Tables                  |            |

|   |      | 5.1.2 Constraint Types                                     |            |

|   |      | 5.1.3 Algebra Types                                        |            |

|   |      | 5.1.4 The TableInput Data Type                             |            |

|   |      | 5.1.5 Table Manipulation Data Types                        |            |

|   | 5.2  | Top Level UI Changes                                       |            |

|   | ٠    | 5.2.1 Simulation Sub-tabs                                  |            |

|   |      | 5.2.2 Moving the Waveform Simulator                        |            |

|   |      | 5.2.3 Dynamic Dividerbar Resizing                          |            |

|   | 5.3  | Generating Truth Tables                                    |            |

|   |      | 5.3.1 Building the Simulation                              |            |

|   |      | 5.3.2 Calculating the Input Space                          |            |

|   |      | 5.3.3 Simulating each Combination                          |            |

|   | 5.4  | Generating Truth Tables for a partial selection of a Sheet | 0          |

|   |      | 5.4.1 Canvas Correction                                    | 0          |

|   |      | 5.4.2 Caching Strategy                                     | 1          |

|   | 5.5  | Filtering with Output Constraints                          | 2          |

|   | 5.6  | Don't Care Reduction                                       | 3          |

|   |      | 5.6.1 Prerequisite Concepts                                | 4          |

|   |      | 5.6.2 Reduction Algorithm                                  | 4          |

|   | 5.7  | Algebraic Truth Tables                                     | 6          |

|   |      | 5.7.1 Definition of the Algebraic System                   | 6          |

|   |      | 5.7.2 Reduction Rules                                      | 9          |

|   |      | 5.7.3 Implementing Algebra                                 | 3          |

|   | 5.8  | Sorting Truth Tables                                       | 6          |

|   |      | 5.8.1 Comparison Function for CellData                     | 7          |

|   | 5.9  | Truth Table Caching and Order of Operations                | 7          |

|   | 5.10 | Rendering the Truth Table                                  | 9          |

|   |      | 5.10.1 Method 1: Using Fulma Tables                        | 9          |

|   |      | 5.10.2 Method 2: Using CSS Grids                           | 0          |

|   | 5.11 | Column-based Operations                                    | 1          |

|   |      | 5.11.1 Moving Columns                                      |            |

|   |      | 5.11.2 Hiding Columns                                      | 1          |

| 6 | Test | ting and Results 6                                         | 3          |

| Ü | 6.1  | Testing Application Stability                              |            |

|   | 0.1  | 6.1.1 Exception Analysis                                   |            |

|   |      | 6.1.2 Failure Analysis                                     |            |

|   | 6.2  | Correctness Testing                                        |            |

|   | 6.3  | Quantitative Performance Testing                           |            |

|   | 0.0  | 6.3.1 Generating Numeric Truth Tables                      |            |

|   |      | 6.3.2 Algebraic Truth Tables                               |            |

|   |      | 6.3.3 Don't Care Reduction                                 |            |

|   |      | 6.3.4 Graphical Manipulation of Truth Tables               |            |

|   | 6.4  | User Experience Testing                                    |            |

|   |      | 6.4.1 Stage 1: Mystery Sheets                              |            |

|   |      | 6.4.2 Stage 2: Questionnaire                               |            |

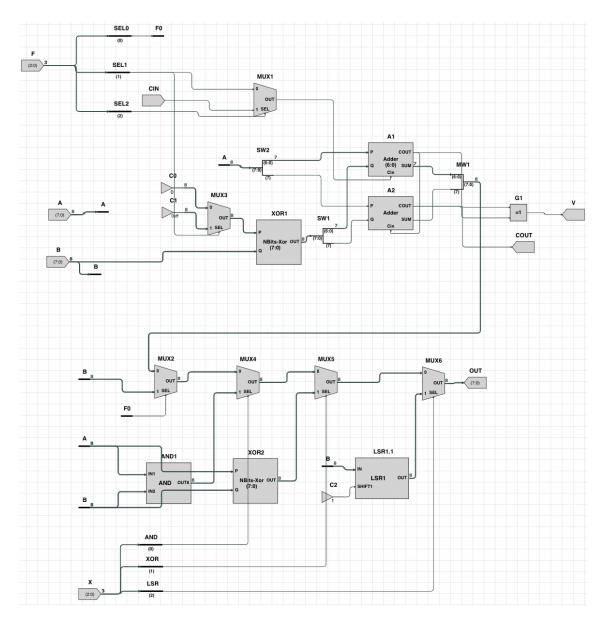

|   | 6.5  | Testing on the 8-bit ALU                                   |            |

| _ | TC . |                                                            |            |

| 7 |      | luation 7.                                                 |            |

|   | 7.1  | Evaluation against Project Aims                            |            |

|   | 7.2  | Evaluation against Issie's Core Principles                 |            |

|   |      | 7.2.1 Robustness                                           |            |

|   |      | 7.2.2 Obviousness                                          | $^{\circ}$ |

|   |      | 7.2.3 Intuitiveness                        | 75 |

|---|------|--------------------------------------------|----|

|   | 7.3  | Evaluation of Application Performance      | 76 |

|   | 7.4  | Comparison Against Issie 3.0.0             | 76 |

|   | 7.5  | Evaluation of Filtering Methods            | 77 |

|   | 7.6  | Evaluation of Reduction Methods            | 78 |

|   |      | 7.6.1 Algebraic Truth Tables               | 78 |

|   |      | 7.6.2 Don't Care Reduction                 | 78 |

|   | 7.7  | Evaluation against Requirements            | 79 |

|   | 7.8  | Summary                                    | 83 |

| 8 | Con  | nclusion and Further Work                  | 84 |

|   | 8.1  | Possible Further Work                      | 85 |

|   |      | 8.1.1 Algebraic Output Constraints         | 85 |

|   |      | 8.1.2 More Algebraic Reduction Rules       | 85 |

|   |      | 8.1.3 Adding Algebra to the Step Simulator | 85 |

|   | 8.2  | User Guide                                 | 85 |

| A | Scre | eenshots of Issie 3.0.0                    | 89 |

| В | Wor  | rk Breakdown Structure                     | 92 |

| C | 8-bi | t ALU Schematic                            | 94 |

# List of Tables

| $\frac{2.1}{2.2}$ | Truth Tables for a 2-bit Multiplexer                                           | 8  |

|-------------------|--------------------------------------------------------------------------------|----|

| 4.1               | Arguments for and against implementing truth-table defined custom components . | 31 |

| 5.1               | Data Types and Structures used for Truth Table Representation                  | 32 |

| 5.2               | Explanation of TruthTable Record fields                                        | 33 |

| 5.3               | Explanation of Fields in the TableInput data structure                         | 36 |

| 5.4               | Average Truth Table Generation and View times with varying Bit Limits          | 38 |

| 5.5               | Time taken by each method to generate a numeric truth table for an 8-bit ALU   | 39 |

| 5.6               | Terminal Value Symbols                                                         | 47 |

| 5.7               | Terminal Operator Symbols                                                      | 47 |

| 5.8               | Non-Terminal Symbols                                                           | 48 |

| 5.9               | New additions to the defined behaviour for each component in fastReduce        | 55 |

| 5.10              | Summary of operations which change the TruthTable data structure               | 58 |

| 5.11              | Time taken to move a column in a Truth Table under different methods (ms)      | 60 |

| 6.1               | Library functions in project code which can throw exceptions                   | 64 |

| 2                 | List of all features which were manually tested                                | 65 |

| 6.3               | Time taken to generate a numeric truth table (ms)                              | 67 |

| 6.4               | Time taken to generate an algebraic truth table for the ALU schematic (ms)     | 67 |

| 6.5               | Time taken to reduce a numeric truth table using Don't Cares (ms)              | 67 |

| 6.6               | Time taken to conduct different graphical manipulations on a truth table (ms)  | 67 |

| 6.7               | Mystery Sheets                                                                 | 69 |

| 6.8               | First set of questions asked in questionnaire                                  | 70 |

| 1                 | Evaluation against Requirements                                                | 80 |

# List of Figures

| 2.1  | The Atkinson-Shiffrin Multi-Store Model                                           | 4  |

|------|-----------------------------------------------------------------------------------|----|

| 2.2  | Algebraic Truth Table in Datasheet for a Three-input Multiplexer [17]             | 8  |

| 2.3  | An example of incomplete Pattern Matching in F#, with a warning from the compiler | 9  |

| 2.4  | How browsers traditionally render HTML using a DOM [33]                           | 12 |

| 2.5  | The Elm Architecture [33]                                                         | 13 |

| 2.6  |                                                                                   | 14 |

| 2.7  | An Overview of Issie's Technology Stack                                           | 14 |

| 2.8  | An overview of Issie's Step Simulation                                            | 17 |

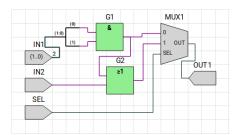

| 4.1  |                                                                                   | 22 |

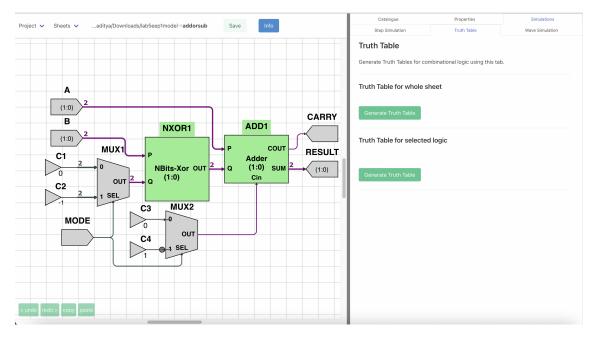

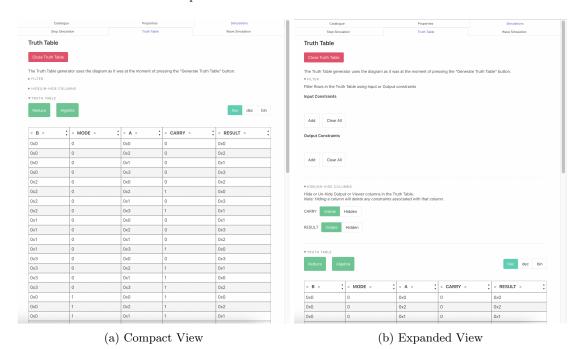

| 4.2  | Contents of Truth Table tab after a truth table has been generated                | 23 |

| 4.3  |                                                                                   | 24 |

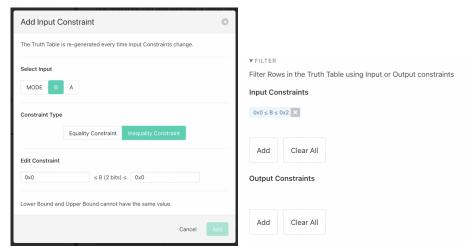

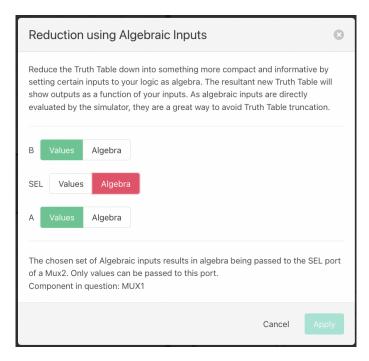

| 4.4  | Adding a Constraint to the Truth Table                                            | 27 |

| 4.5  | Algebra Input Selector popup                                                      | 29 |

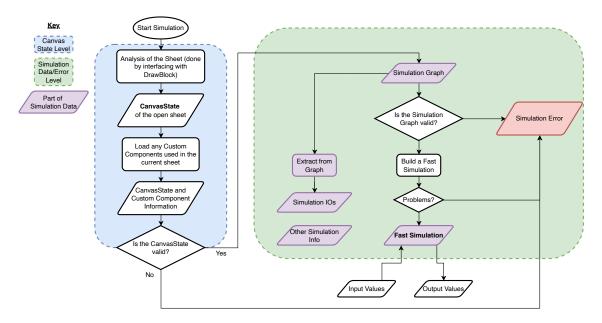

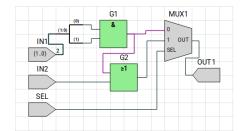

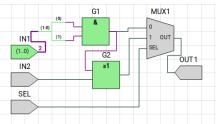

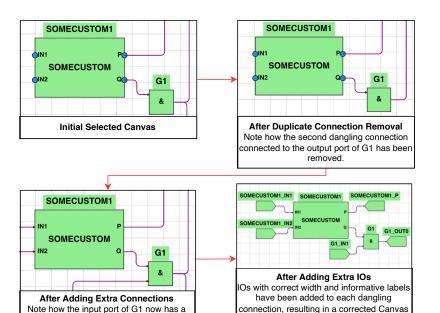

| 5.1  |                                                                                   | 35 |

| 5.2  |                                                                                   | 42 |

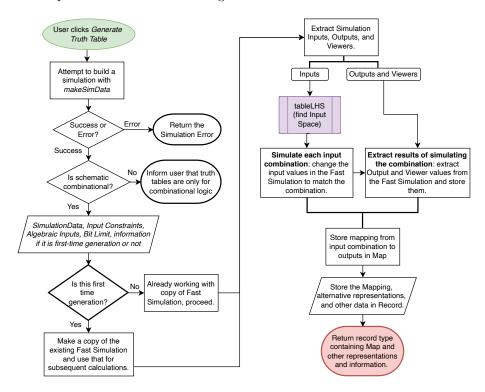

| 5.3  | 1                                                                                 | 42 |

| 5.4  |                                                                                   | 43 |

| 5.5  |                                                                                   | 44 |

| 5.6  | 1 0 0 0                                                                           | 49 |

| 5.7  |                                                                                   | 50 |

| 5.8  | Ç [ ]                                                                             | 51 |

| 5.9  |                                                                                   | 53 |

| 5.10 | 01 1 0                                                                            | 54 |

|      |                                                                                   | 56 |

| 5.12 | How operations update the Truth Table                                             | 59 |

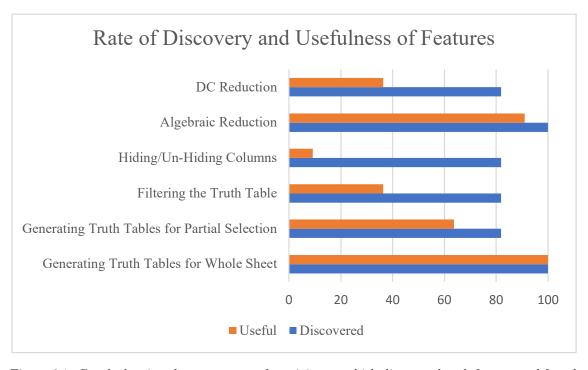

| 6.1  | Graph showing the percentage of participants which discovered each feature and    |    |

|      |                                                                                   | 70 |

| 6.2  | First 18 rows of the Algebraic Truth Table for 8-bit ALU                          | 72 |

| A.1  | 1 0                                                                               | 89 |

| A.2  | \                                                                                 | 90 |

| A.3  |                                                                                   | 90 |

| A.4  | Issie's Waveform Simulator                                                        | 91 |

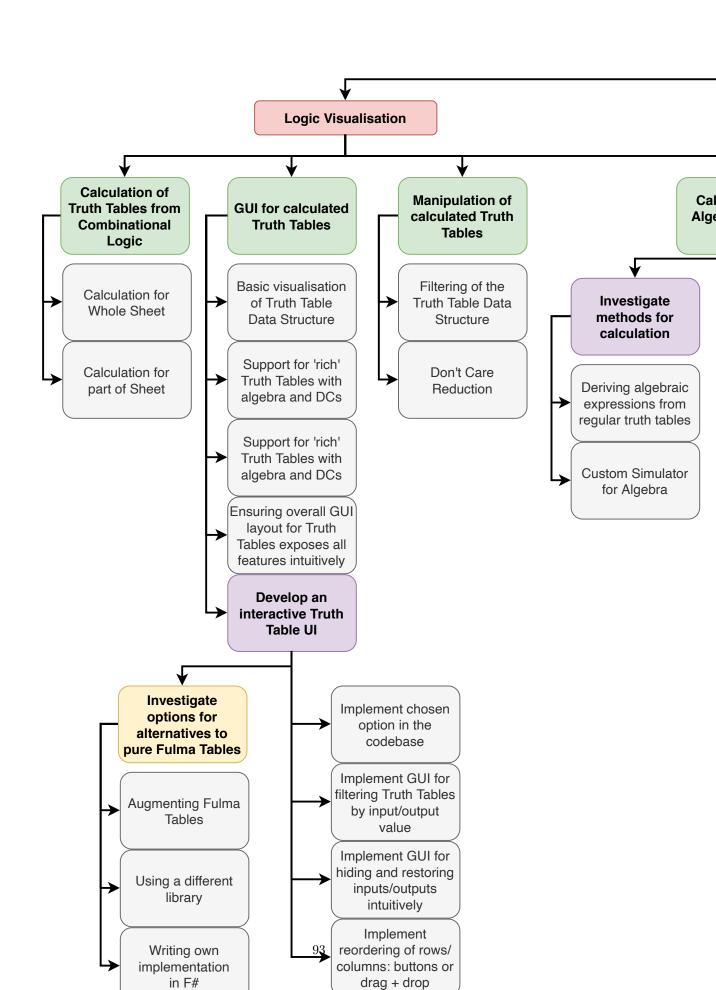

| В.1  | Work Breakdown Structure with ordered backlog                                     | 93 |

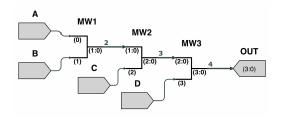

| C.1  | Schematic Diagram for an 8-bit ARM ALU                                            | 95 |

# Table of Acronyms

| Acronym                      | Definition                                             |  |  |  |  |  |  |  |

|------------------------------|--------------------------------------------------------|--|--|--|--|--|--|--|

| ALU                          | Arithmetic Logic Unit                                  |  |  |  |  |  |  |  |

| CLR                          | Common Language Runtime                                |  |  |  |  |  |  |  |

| CSS                          | Cascading Style Sheets                                 |  |  |  |  |  |  |  |

| DC                           | Don't Care                                             |  |  |  |  |  |  |  |

| DOM                          | Document Object Model                                  |  |  |  |  |  |  |  |

| GUI                          | Graphical User Interface                               |  |  |  |  |  |  |  |

| HTML                         | Hypertext Markup Language                              |  |  |  |  |  |  |  |

| ISSIE                        | Interactive Schematic Simulator with Integrated Editor |  |  |  |  |  |  |  |

| MVU                          | Model View Update                                      |  |  |  |  |  |  |  |

| UI                           | User Interface                                         |  |  |  |  |  |  |  |

| UWP                          | Universal Windows Platform                             |  |  |  |  |  |  |  |

| WBS Work Breakdown Structure |                                                        |  |  |  |  |  |  |  |

| WPF                          | Windows Presentation Foundation                        |  |  |  |  |  |  |  |

## Chapter 1

## Introduction

### 1.1 Project Motivation

Digital Electronics and circuit design are core fields in the study of Electronic Engineering and are focused on the analysis and logical interpretation of digital signals, as well as the engineering of hardware that manipulates them in accordance with a desired logical function. A strong understanding of the fundamentals of digital electronics and circuit design serve as a foundation for multiple branches of study within Electronic Engineering. Therefore, it is vital that undergraduate students at Imperial College and other institutions have the best tools available to aid their study of these fundamental concepts. One of the many challenges a first-year undergraduate student may face while learning Digital Electronic design is conceptualising relationships between inputs and outputs, and how these relationships relate to design specifications. At Imperial College London, EE students have the opportunity to gain a deeper insight into combinational logic through practical laboratory sessions, during which they create and simulate combinational circuits. The tools which they use must fulfil two criteria; firstly they must provide an education-focused platform through which students can learn more about combinational logic and hardware design; secondly they must be capable design tools in their own right which allow students to design and simulate complex logic.

Issie (Interactive Schematic Simulator with Integrated Editor) [1], an intuitive hardware design application, was developed at Imperial College London to address the lack of third-party programs that matched the above criteria. Issie is designed to be easy to use (requiring no user manual) and informative; visual cues and clear error messages guide students towards correct designs while individual step and waveform simulators allow students to vary inputs and see the effect on output values. This allows them to gain a better understanding of the hardware logic they have created. However, there is room for improvement. In its current form, users of the application implement digital logic by building it component-by-component on a schematic diagram. Any syntactically correct digital circuit can be simulated using the *Step Simulator*. In the Step Simulator, users specify values for each input to the digital logic, and can read the corresponding output values. Intermediate values can also be observed using *Viewer* components. This functionality enables the user to easily verify their schematic with specific test cases, but lacks the ability to clearly summarise and verify the overall relationship between the inputs and outputs of the logic circuit. Users must therefore gain an overall understanding of the circuit through a combination of:

- 1. Visually analysing the schematic to understand its logical function.

- 2. Entering different input combinations into the Step Simulator and analysing the effect each change has on the outputs.

As the implemented digital logic grows in complexity, the relationship between the inputs and outputs often becomes more obscure, and the schematic itself grows in size and can start to feel divorced from the specification. In such situations, the aforementioned method for understanding the logic circuit becomes less effective. To stop the schematic from getting too large and crowded Issie lets users define hierarchical *Custom Components* which modularise the schematic and cut down on logic duplication. For example, an ALU may be implemented as a Custom Component

within a CPU design schematic. This feature however, does not fully combat the issue of obscure relationships between inputs and outputs for complex circuits. Firstly, custom components that are not named clearly further obscure the logic function of the circuit. Secondly, due to their hierarchical nature, custom components can be nested inside other custom components, meaning that the user may have explore multiple layers of nested components before they can analyse the top-level schematic. This is a time-consuming exercise, requiring significant effort by the user. Therefore, there is significant value to adding functionality to Issie which allows users to better understand the relationships between inputs and outputs in digital logic circuits in a shorter amount of time.

One possible solution to this problem is automatically generating truth tables from the schematic. Truth tables exhaustively show the relationship between all inputs and outputs in an organised, persistent format. Inspecting cases in a truth table is far quicker than repeatedly changing values in the Step Simulator. Furthermore, by investigating novel ways of presenting and interacting with these truth tables their value addition to the learning and circuit design experience in Issie can be boosted. For example, the ability to present relationships inferred from the schematic in the truth table, or reduce an existing truth table with user-defined constraints, would provide the user with far more information than a simple simulation.

There is also merit in investigating the reverse; generating schematics from user-entered truth tables. This could reduce time spent designing hardware components which implement simple logic but require many gates and connections, as well as serve as a stepping stone between schematic design and HDL-based design.

Thus, there is a strong case for finding and implementing alternative ways to visualise (and possibly input) combinational logic in Issie to enable users to gain a better understanding of relationships in the logic, as well as the specification of the top-level design. If added in a way which compliments Issie's existing features, such enhancements are likely to increase Issie's effectiveness as an educational platform in addition to its capability as a digital logic design tool. This will benefit students at Imperial College and other educational institutions.

## 1.2 Project Definition

The purpose of this project is to explore novel ways in which interactivity can be added to automatic schematic-derived truth tables, and how interactively generated truth tables can be used as a fast aid to design combinational logic. This is to achieve the overall aim of this project - to improve Issie in such a way that it is easier for students to understand the use of combinational logic in digital design. The deliverable will be integrated as an extension to the Issie application, with users being able to generate truth tables from the schematic and interact with them in ways that will augment their understanding of the logic they are designing and of Digital Electronics concepts in general. This project will conduct a short evaluation of Issie, highlighting the areas where it can be improved. While the primary focus of the project is on visualising combinational logic with interactive truth tables, the project will also seek to improve the overall user experience of Issie in other ways such as tweaking/redesigning elements of the UI or changing how information is communicated to users such that it is consistent and clear. In addition to improving the user experience for Issie, this project also aims to improve the developer experience wherever possible. Since its inception, maintainability and extensibility have been key to Issie [2]; therefore the code contributed to the Issie repository should be well-documented, readable, and interface well with existing code so that it is easy for future Issie developers to maintain and extend it. Further to this, if an appropriate opportunity arises, the project should also aim to reduce technical debt within the existing codebase.

#### 1.2.1 Core Principles of Issie

As this project aims to improve Issie, any work done on this project should align with Issie's core principles. All features implemented in Issie must be:

1. **Robust:** Software is robust when it is able to handle errors and behave correctly under exceptional circumstances, such as when supplied with erroneous inputs [3]. For simulations

and text field inputs, Issie notifies the user of the nature of the error. User input, no matter how malformed, must never crash the application or lead to undefined behaviour.

- 2. **Obvious:** The visual output given to the user should make it obvious what is happening without the need for unnecessary explanation. Issie prefers to *show not tell* in order to remain beginner-friendly. For example, Issie uses colour-coded popups and highlights to draw user attention where it is needed and communicate events clearly.

- 3. **Intuitive:** All functionality must be easy to expose to the user there should be no need for detailed user guides as the UI for all functionality must be designed in a way such that users can intuitively learn how to use all of the application's features.

In addition to these core principles, any extensions this project makes to Issie must also take into account the targeted users and the intended primary use case - teaching undergraduate students in a university laboratory while also enabling students to carry on where they left off at home. Thus, all new features must be cross-platform compatible and be suitable for students working in a laboratory and working alone at home.

In conclusion, this project has two final deliverables. The first is an improved version of Issie, while the second deliverable consists of appropriate documentation of added features, and improvements to the documentation of existing features.

## Chapter 2

## Background

This chapter describes various theoretical concepts which provide context to many of the decisions made throughout the duration of the project. It also describes and evaluates the current version of Issie, analysing its strengths and weaknesses. Given the overall project goal of improving combinational logic visualisation in Issie, this analysis provides context for the extensions made to Issie by the project, which are described in subsequent chapters.

### 2.1 Pedagogical Considerations

Given the overall project aim of making it easier for students to understand the use of logic in digital design, any features added to Issie must enhance the learning experience of its users. Many decisions related to the project, such as which features to add, the UI/UX design, and the level of interactivity will all be made through the lens of pedagogy.

#### 2.1.1 Memory Models

One of the key facets of learning is the long-term retention of key concepts and relationships. The Atkinson-Shiffrin multi-store model [4] provides a good framework for modelling the workings of human memory, and many task-specific models, theories, and techniques have been derived from it. The aim of any effective learning application should be to convey and revisit information in such a way that it succeeds in reaching the Long Term Memory store.

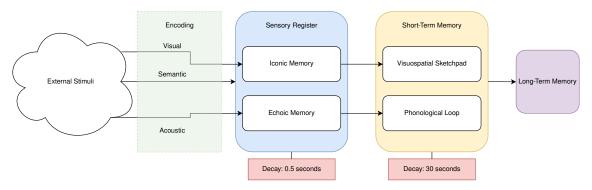

Figure 2.1: The Atkinson-Shiffrin Multi-Store Model

As shown in Figure 2.1, the Atkinson-Shiffrin Multi-Store Model states that humans perceive information through external stimuli, and that information is encoded as three different types of stimulus. **Visual** encoding encodes information in pictures and diagrams, **Semantic** encoding encodes information in words and their meanings, while **Acoustic** encoding encodes information in sounds. This encoded information is processed by the sensory register. If attention is paid to this information, it travels into short-term memory, otherwise it decays within half a second and is forgotten. For information to progress from short-term to long-term memory, a process

of repetition called maintenance rehearsal is necessary [5], in which the information is repeated within the learner's mind. For visually encoded information, this could be through repeated visualisation of diagrams or patterns in what the learner sees on a screen, while for acoustically encoded information this is achieved through the learner playing back the soundbite in their head (phonological loop). A key take-away from this memory model is that human brains process different information encodings independently, meaning that even if one encoding type is saturated with information, additional information can still be conveyed to the learner using an alternative encoding method.

In its current form, Issie encodes information about the digital circuit both visually (circuit diagram, error highlighting etc.) and semantically (error messages, simulation outputs). No information is encoded acoustically, however outside of chimes for errors there is not much scope for implementation of sounds. Furthermore, students will receive plenty of auditory information in the form of teaching from lab assistants and conversation with their peers. Any extensions added to Issie by this project should therefore focus on conveying information to users through a combination of diagrams with appropriate annotations and informative text.

#### 2.1.2 Educating Engineers

As a tool for teaching Digital Electronics, Issie's primary user base is engineering students. Therefore, there is value in exploring trends in how engineers learn best, and tailoring Issie's design and structure to align with these trends. In 1992, Fleming and Mills proposed that there were four categories of how students learned. These are visual, auditory, reading/writing, and kinesthetic [6]. Most learners will learn using all of these methods, however will exhibit a preference towards one or two. Studies have shown that engineers have a preference towards visual and kinesthetic learning techniques [7]. The visual aspect means that engineers prefer information be conveyed to them through diagrams, patterns, and highlighted meaningful symbols. On the other hand, the kinesthetic aspect means that engineers prefer to learn through demonstrations, simulations, and their own experiences. The existence of practical lab sessions and Issie itself lends itself to a focus on kinesthetic learning; students explore concepts they have been taught about in lectures by building and simulating combinational logic. Therefore, the results of the VARK survey concur with the current teaching style in the EEE Department at Imperial College. Currently, Issie has an interactive diagram with highlighting (visual encoding), as well as simulators for testing logic and general experimentation (kinesthetic learning). Thus, it can be said that Issie in its current form is fit for its purpose: educating engineers. In turn, any extensions added to Issie by this project should continue this trend of visual and kinesthetic learning, but while also taking care to not overload the users' sensory register and short-term memory.

#### 2.1.3 Cognitive Theories of Self Efficacy and Constructivism

There are more factors that contribute towards an effective learning experience than just the conveyance of information. The learning process must be structured in such a way that students remain motivated while learning complex concepts. A ten-year longitudinal study [8] found that there is a significant correlation between students who are motivated, therefore having high self-confidence, and academic attainment. Therefore, while developing educational tools like Issie, an emphasis must be placed on communicating information to students in such a way that they retain the belief that they can successfully learn the content. This approach aligns well with the theory of constructivism in education, which seeks to educate students by having them discover knowledge intuitively in contrast to traditional methods in which a student is considered an 'empty vessel' waiting to be filled up by a teacher [9]. The rationale behind the theory is that this self-discovery of knowledge will build a stronger conceptual understanding of what is being learnt. Constructivism aligns well with teaching styles that suit kinesthetic learners, as both approaches focus on students learning through their own experiences. Engineers tend to be kinesthetic learners, therefore, this project should aim to improve Issie in such a way that students are able to interactively and iteratively build their understanding of digital electronics and circuit design by themselves.

### 2.2 Combinational Logic

Combinational logic is a type of digital logic in which the output of the logic is a pure function of its present inputs [10]. This means that combinational logic is memoryless; it is not affected by any previous outputs. This is in contrast to sequential logic, for which the output is dependent on present input values and some internal state derived from previous outputs.

#### 2.2.1 Visualising Logic with Boolean Algebra

The aforementioned pure function which maps inputs to outputs can be written as a Boolean expression. A Boolean expression, much like traditional mathematical expression, features a set of input terms combined using operators. There exist three fundamental Boolean operators [11]:

NOT, a unary operator which outputs the inverse of the input.

**AND**, a binary operator which outputs HIGH when both inputs are HIGH and LOW otherwise. Denoted by

**OR**, a binary operator which outputs HIGH when either of the inputs are HIGH, and LOW otherwise

Other Boolean operators, such as NAND, NOR, and XOR also exist, but can be defined using a combination of the three fundamental operators. Therefore, the first and most basic way of visualising combinational logic is simply through writing the Boolean expression which represents it. However, it can be difficult to quickly understand what some logic does using just Boolean expressions. Take for example the following Boolean equation for output Y, derived from inputs S, A, and B:

$$Y = \overline{S}.A + S.B \tag{2.1}$$

While the operations performed are clear, it may not be very clear on first inspection to an inexperienced student what the expression actually achieves. Furthermore, Boolean expressions grow in complexity as schematics become larger, making them even tougher to understand at a glance.

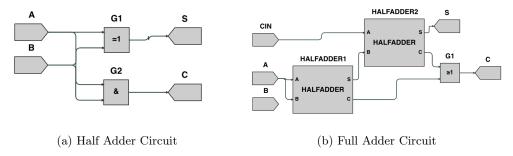

#### 2.2.2 Visualising Logic with Schematic Diagrams

Schematic diagrams give the hardware representation of the combinational logic, and are the primary way of creating and visualising combinational logic in Issie. At their simplest, they consist purely of logic gates; these gates each correspond to a Boolean operator. However, in practice (and Issie) schematics are at a slightly higher-level, with certain combinational components (which can be built from gates) pre-created for the user. For example, Equation 2.1 represents a 2-bit Multiplexer, which is a component available in Issie's catalogue. The recall of stored knowledge due to the visual stimulus of the multiplexer component on the diagram is much more likely compared to the semantic stimulus of the Boolean expression. However, as a schematic increases in size, the number of components may become so large that holding all of the visual stimuli in short-term memory is unfeasible. Issie combats this by letting users modularise their schematic through hierarchical custom components. Alongside decreasing schematic size and repeated logic, this feature actually aims to teach students the technique of modularising their work (whether that is a schematic or code), and its advantages. These advantages [12] include efficient development, easier dubugging, and logic reuse. However, as mentioned in the Project Motivation, hierarchical components are not always effective (particularly if badly named and organised), leaving a opportunity for improvement through complementary visualisation techniques.

#### 2.3 Truth Tables

A truth table represents a given combinational logic function; featuring all input combinations on the left, and their corresponding output(s) on the right. As the truth table maps all possible inputs to their output, it is trivial to look up the behaviour of the logic in a given scenario. A very basic example is the truth table for the Boolean **AND** operator, shown in Table 2.1.

| $\mathbf{A}$ | B | C |

|--------------|---|---|

| 0            | 0 | 0 |

| 0            | 1 | 0 |

| 1            | 0 | 0 |

| 1            | 1 | 1 |

Table 2.1: Truth Table for the Boolean AND operator (C = A.B)

Given that a truth table defines some logic using an exhaustive set of examples, it could be said that truth tables are ideal for kinesthetic learners. This exhaustive property can also be used to test for logical equivalence. Suppose the claim is made that two schematics, with one schematic featuring far fewer components than the other, are logically identical. Equivalence could be confirmed by simply checking if the truth tables for the two schematics are the same.

However, a disadvantage of using truth tables to visualise combinational logic is that they can very rapidly grow in size. For logic with n single-bit inputs, the number of rows in the associated truth table is  $2^n - 1$ . For multi-bit inputs this number would grow even larger. Thus, Issie schematics with a large number of inputs would result in very long truth tables, which would likely intimidate the user. The size of generated truth tables could be reduced by filtering them based on user selections, or through truth table reduction methods.

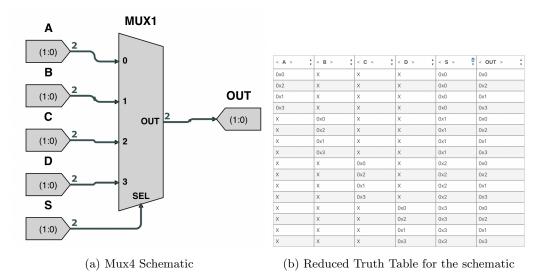

#### 2.3.1 Reduction using Don't Cares

A "Don't Care" term in a truth table can mean different things based on it's positioning. It is more commonly seen on the right-hand side of a truth table, signifying that an output for a given input combination is invalid or has no use [13]. This information is often used when attempting to simplify Boolean expressions using Karnaugh maps. On the other hand, a Don't Care term in an input row signifies that the particular input has no effect on the eventual output of the logic for that combination. These Don't Care inputs can be found through logic minimisation, of which there are numerous techniques ranging from the aforementioned Karnaugh Maps [14] to heuristic-based tools like Espresso [15]. The latter is very effective at reducing large circuits efficiently, and would therefore appear to fit the needs of the project well. An example of the reduction can be seen in Table 2.2, where the eight row exhaustive truth table (2.2a) is reduced to two rows (2.2c). However, Espresso and other common minimisation techniques treat their inputs and outputs as single-bit Boolean values which are either ON, OFF, or DC - corresponding to 1, 0 and Don't Care [16]. Multi-bit IOs are broken into their constituent bits. In Table 2.2c, only HIGH outputs are shown – this works when it can be assumed that all other input combinations yield 0. This approach aligns well with industrial applications, where signals on wires can only be HIGH or LOW, and there is value in reducing to the form which requires the fewest gates. On the other hand, Issie is an educational application where inputs and outputs can have more than two values, and focus is more on semantics and understanding rather than the most cost-efficient hardware design. Therefore, such minimisation would not integrate well with Issie's existing implementation of multi-bit IOs.

In order to implement DC reduction in Issie, a suitable algorithm will have to be written which supports multi-bit inputs. One possibility may be analysis of redundancies in the existing truth table. For example, in the full truth table, the first and third row both have an output value of 0, with the only difference being the change in the value of B. Given that B can only take two values, this shows that when A=0 and S=0, the value of B does not affect the output - therefore we "don't care" about B. Rows one and three can therefore be collapsed into one row, with the entry for the B column being replaced with an "X". This process can be repeated until all such row combinations have been collapsed. The results from this process can be seen in Table 2.2b. The length of the truth table has been reduced by 25%, and the actual semantic function of what the multiplexer does is much clearer as well. This table is however, much larger than the reduced table generated by Espresso, indicating that it may not work well with larger schematics.

#### 2.3.2 Algebraic Truth Tables

While reduction with Don't Cares is useful, neither implementation of it is ideal. Industry-style minimisation doesn't fully align with Issie's implementation, while custom algorithms may not be reduce the table enough. Additionally, Don't Care reduction cannot simplify relationships which involve all inputs, such as arithmetic. A viable alternative is an Algebraic Truth Table; these are often found on component datasheets [17] and have the task of summarising the behaviour of the circuit in a concise and readable format. One such example is shown in Figure 2.2, which is an excerpt from a datasheet for a three-input multiplexer. H and L are equivalent to 1 and 0, but the terms of form  $I_x$  in the table are algebraic values representing inputs. The select signals (S2, S1, S0), which actually control the circuit behaviour are still numeric.

| TRUTH TABLE |        |         |                  |                |                |  |  |  |

|-------------|--------|---------|------------------|----------------|----------------|--|--|--|

|             |        | OUTPUTS |                  |                |                |  |  |  |

|             | SELECT | 7       |                  |                |                |  |  |  |

| S2          | S1     | S0      | OUTPUT ENABLE OE | Y              | Ŧ              |  |  |  |

| Х           | Х      | Х       | Н                | Z              | Z              |  |  |  |

| L           | L      | L       | L                | I <sub>0</sub> | Īō             |  |  |  |

| L           | L      | н       | L                | I <sub>1</sub> | Īī             |  |  |  |

| L           | н      | L       | L                | I <sub>2</sub> | Ī <sub>2</sub> |  |  |  |

| L           | н      | н       | L                | l <sub>3</sub> | Ī₃             |  |  |  |

| Н           | L      | L       | L                | 14             | Ī4             |  |  |  |

| Н           | L      | н       | L                | I <sub>5</sub> | Ī <sub>5</sub> |  |  |  |

| Н           | н      | L       | L                | 16             | Īē             |  |  |  |

| Н           | н      | н       | L                | l <sub>7</sub> | ĪŦ             |  |  |  |

H = High logic level, L = Low logic level, Z = High impedance (off), X = Irrelevant, I<sub>0</sub>, I<sub>1</sub>...I<sub>7</sub> = The level of the respective input

Figure 2.2: Algebraic Truth Table in Datasheet for a Three-input Multiplexer [17]

Table 2.2d shows what the corresponding algebraic truth table would look like for the running example in this section. A is propagated to the output when the selection input (S) is low, and B is propagated when S is high. This clearly describes a two-input multiplexer. Having functionality which could create similar tables for user-created schematics, with support for more complex algebraic operators would likely be useful. This is because algebraic truth tables carry far more semantic information in a much smaller visual space, meaning that a students' sensory register is less likely to be overloaded.

| $\mathbf{A}$ | В      | $ \mathbf{S} $ | OUT   |                   |                 |                        |     |                  |                |              |     |         |                |                        |           |

|--------------|--------|----------------|-------|-------------------|-----------------|------------------------|-----|------------------|----------------|--------------|-----|---------|----------------|------------------------|-----------|

| 0            | 0      | 0              | 0     | _                 |                 |                        |     |                  |                |              |     |         |                |                        |           |

| 0            | 0      | 1              | 0     | $\mathbf{A}$      | В               | $\mid \mathbf{S} \mid$ | OUT |                  |                |              |     |         |                |                        |           |

| 0            | 1      | 0              | 0     | 0                 | X               | 0                      | 0   | _                |                |              |     |         |                |                        |           |

| 0            | 1      | 1              | 1     | X                 | 0               | 1                      | 0   |                  |                |              |     |         |                |                        |           |

| 1            | 0      | 0              | 1     | X                 | 1               | 1                      | 1   |                  |                |              |     |         |                |                        |           |

| 1            | 0      | 1              | 0     | 1                 | X               | 0                      | 1   | ${f A}$          | $ \mathbf{B} $ | $\mathbf{S}$ | OUT | ${f A}$ | $ \mathbf{B} $ | $\mid \mathbf{S} \mid$ | OUT       |

| 1            | 1      | 0              | 1     | 0                 | 0               | X                      | 0   | 1                | X              | 0            | 1   | A       | В              | 0                      | A         |

| 1            | 1      | 1              | 1     | 1                 | 1               | X                      | 1   | X                | 1              | 1            | 1   | A       | В              | 1                      | В         |

| (a)          | Full 7 | Truth          | Table | (b) DC<br>(Inc. Z | C Red<br>Zeros) |                        |     | (c) DC<br>(Espre |                | uced         |     | (d) Ala | gebra          | ic Tr                  | uth Table |

Table 2.2: Truth Tables for a 2-bit Multiplexer

### 2.4 An Overview of Issie's Technology Stack

The reasoning and process behind the decisions made for Issie's technology stack can be found in Marco Selvatici's dissertation on DEFlow, the predecessor to Issie [2]. This section describes the technology stack, and evaluates and reaffirms why Issie's technology stack is well suited.

#### 2.4.1 Programming Language

Issie is written in F#, an open-source, cross-platform, interoperable programming language for writing succinct, robust and performant code [18]. It is functional-first; meaning that it contains many features found in functional languages and encourages a functional programming style while also allowing programmers the flexibility to use the programming styles of other paradigms. Pure functional programming languages adopt a philosophy of declarative programming and immutable data; data values cannot be updated after initial assignment, and functions take this data as input and map it to output data. These functions are deterministic, meaning that their output is solely dependent on the value of their inputs and that there is no internal state affecting the behaviour of the function. This differs from the more common imperative style of programming where code is treated as a sequential list of instructions which mutate program data/state. The deterministic nature of functions in pure functional programming makes them very easy to understand, as operations on data have no side-effects and are therefore very easy to track. Not only does this make debugging easier, but it leads to fewer overall bugs in the code. A large-scale study of programming languages and code quality on Github [19] found that "Functional languages have a smaller relationship to defects than other language classes, whereas procedural languages are either greater than average or similar to the average." The study also found that the "Functional-Static-Strong-Managed" class of languages (i.e. languages that are functional, statically and strongly typed with in-built memory management) are less likely than average to result in defect-fixing commits on Github. While not a part of the study, F# does belong to this class of languages, and is therefore a wise choice of programming language for Issie. F# features a Hindley-Milner type system, which has a provably sound type inference algorithm [20]. Type inference allows for F# to be statically typed while eliminating the need for type annotations in the code. This results in clean-looking and succinct code while still maintaining the benefits of static typing. Furthermore, as types can be inferred on the fly by IDEs such as Visual Studio, it is much easier for the programmer to track the correctness of the program.

```

Red

Orange

Yellow

Green

Indigo

Violet

et printColor color =

atch color with

RainbowColor.Red -> printfn "Red"

RainbowColor.Orange -> printfn "Orange

RainbowColor.Yellow ->

printfn "Yellow'

RainbowColor.Blue -> printfn "Blue

printfn "Indigo'

RainbowColor.Indigo

RainbowColor.Violet -> printfn "Violet"

```

Figure 2.3: An example of incomplete Pattern Matching in F# , with a warning from the compiler

One such example is found when pattern matching, as seen in Figure 2.3. The function printColor takes as input some colour of the rainbow (type RainbowColor) and prints the colour. RainbowColor is an F# Discriminated Union (DU) type [21], where the data stored in the value is not fixed; it can be one of several distinct options. DU types have many applications, ranging from representing valid and error cases to small object hierarchies. The type system allows for the IDE to first infer the type of the variable color, and then realise that the pattern match does not cover the DU case for when color is Green. Mousing over the warning line in Visual Studio gives the following message: "Incomplete pattern matches on this expression. For example, the value 'Green' may indicate a case not covered by the pattern(s)."

Such hints are immensely useful for the programmer. The advantage of such checks being performed before and at compile-time is that it decreases the number of errors at run-time, which tend to be more disruptive.

F# also helps protect against runtime errors through the use of Monadic types. Sometimes, certain actions in a program may need to return nothing, such as an unsuccessful lookup in a Map/Dictionary or if there is an absence of some data. Usually such messages are communicated within the

program using either exceptions or NULLs which have to be caught and handled. If not tracked and handled appropriately, NULLs in particular can lead to some very nasty and hard-to-debug runtime errors. F# allows programmers to minimise the use of exceptions and avoid the use of NULLs using the Option and Result types. The Option type can take the value Some <type a> or None, giving the programmer a safe way to indicate nothing without using NULLs. The Result type can reflect success (Ok <type a>) or failure (Error <type b>), giving the programmer a safe way to propagate errors through their code without raising exceptions or returning NULL.

While F# has the many features and benefits of pure-functional languages and strongly encourages the programmer to use them, it is an impure functional language and does allow the programmer to use other styles of programming. For example, mutable state in functions is allowed by the use of the mutable keyword upon definition. This allows flexibility; programmers can use the default functional style in most places, and can selectively choose where to introduce functionally impure constructs such as mutable state. An example of this in Issie is the FastSimulation used by the Step Simulator, which uses mutable arrays to represent the value of component inputs/outputs at different clock cycles.

As most of the features mentioned in this section are either unique to or far better implemented in F# compared to other common app development languages such as JavaScript or Python, and that F# belongs to the most bug-free class of languages, it can be said that Issie's choice of programming language is apt and ideal.

#### 2.4.2 Ecosystem

While originally built as a language for the .NET framework, built to run on the Microsoft Common Lanuage Runtime (CLR) [22], F# can also execute in Javascript environments through the use of third-party trans-compilation tools [23]. Therefore, F# can be used to build desktop applications using .NET, as well as Javascript web apps. Issie is built using the latter method; F# code is compiled to JavaScript, which is executed in a desktop environment through Electron. This section describes the chosen tools in this process, and the reasoning behind those choices.

#### Electron

Electron [24] is a framework for building desktop applications using JavaScript, HTML, and CSS. Electron comes bundled with the open-source Chromium browser and Node.js, a runtime environment that lets JavaScript code execute outside of a browser. Using these, Electron enables web apps to run locally on the user's machine outside of a web browser, akin to a native program. The advantage of this approach is that a developer can create a cross-platform application without any experience of programming native applications for any platform. On the other hand, pure native desktop applications often require differing codebases if multiple platforms are to be targeted [25]; this is a far more labour-intensive approach which also requires a wider skill set. Common native desktop application technologies, such as UWP and WPF, have a much steeper learning curve compared to Electron as well [26]. Given that Issie is maintained by various students over time, an ecosystem that allows for easy cross-platform development with a relatively shallow learning curve is preferable, making Electron well suited for Issie's ecosystem.

However, potential issues with Electron must also be discussed. As Electron apps bundle Chromium and Node, they are often quite large. Additionally, due to the use of the RAM-intensive Chromium browser, Electron apps tend to use more memory than other similar applications [27]. This could lead to decreased performance on low-end hardware. Electron is also dependent on a large amount of open-source code, and web apps are often very reliant on Node dependencies, which can change at any time. This reliance could also be perceived as a weakness.

However, despite some of its shortcomings, Electron is still a good fit for Issie's use case. Issie in its current form is performant, responsive, and stable; implying that the performance issues with Electron have not affected Issie significantly enough for there to be notable issues. The advantage of easy cross-platform development, as well as good integration with Fable (which allows F# to be used as the programming language), outweighs the risks posed by potential Node dependency issues, as well as a larger app footprint.

#### **Fable**

While Electron provides a convenient framework for building cross-platform applications, it requires a JavaScript codebase. JavaScript is a weakly and dynamically typed imperative language - making it a sub-optimal choice for the development of Issie. The gap between development and deployment is bridged by **Fable** [23], a compiler that brings F# to the JavaScript ecosystem. Fable compiles F# to clean JavaScript code which can run under Electron. Fable also includes bindings for React [28], a highly performant JavaScript library for building user interfaces; this allows Issie's F# code to create React elements which Fable will compile to their respective JavaScript implementations.

#### 2.4.3 User Interface and Rendering

A well-written and structured Graphical User Interface (GUI) is an essential component of any application, but it becomes even more vital in the context of an application like Issie which prioritises an interactive and intuitive interface. In Issie, most of the user's interaction with the program is done using the mouse; clicking, dragging, and hovering. This means that the UI code must be able to handle a constant stream of pseudo-random mouse events and deal with them quickly and appropriately. It must also be maintainable and extensible to easily allow for more functionality to be added over time. This section describes the workings of Issie's UI framework, as well as the reasoning behind the decision to choose the framework.

#### Elm, Elmish, and MVU

The Elm Architecture [29], also known as the MVU Architecture, is a pattern for creating interactive programs which emerged from the Elm programming language. Elm [30] is a purely functional language for creating websites and web apps. Elm compiles to JavaScript - this is similar to how using F# with Fable allows functional F# code to be compiled to JavaScript for a web app. Issie uses the Elmish library [31], which brings Elm's MVU architecture to F# and integrates well with Fable, enabling Issie's smooth and robust GUI.

The MVU architecture gains its name from the three parts it splits the UI code into:

**Model:** A data structure which stores the state of the application. In Issie this is a very large record, containing lots of information ranging from the results of a simulation to which components are selected and highlighted.

**View:** A pure function which specifies how the information in the model (application state) should be displayed to the user. The developer writes a function to turn the model into HTML/CSS equivalents, and Elm (or Fable if using F# with Elmish) converts this to actual HTML/CSS and renders it.

**Update:** A way to update the application state triggered by events such as user input. These events are communicated within the program using *messages*, which are triggered by the user interacting with the GUI. The update function is a pure function which accepts two parameters, the incoming message and the current model. It then interprets the message and returns an updated version of the model.

An initial Model is specified in the code, which is rendered by the View function on application startup. The user can then interact with the application - each interaction will generate a message which is passed to the update function. The update function processes this message and, if required, will return an updated model which reflects the effects of the interaction. On its next invocation, the View function will render this updated application state, showing the user the result of their interaction.

The MVU Architecture has numerous strengths, many of which make it suitable for use in Issie. It's structure, based on an immutable Model with deterministic (pure) View and Update functions, means that data flows in only one direction through the whole application, while events which warrant a change in the application state are clearly marked as messages. This making the rendering process easier to understand for the programmer [32], meaning that more time is spent writing useful code instead of debugging. This is unsurprising given that Elm, like F#, is a functional language, and therefore belongs to the "Functional-Static-Strong-Managed" class of languages mentioned in Section 2.4.1. F# also has features which integrate well into the MVU

architecture, strengthening it further. One such example is F#'s strict compile order, which helps avoid cyclic references between view subfunctions [32]. Altogether, the MVU architecture is a good fit for Issie, improving the developer experience while delivering a performant UI.

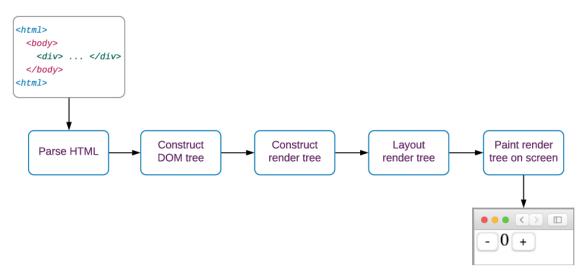

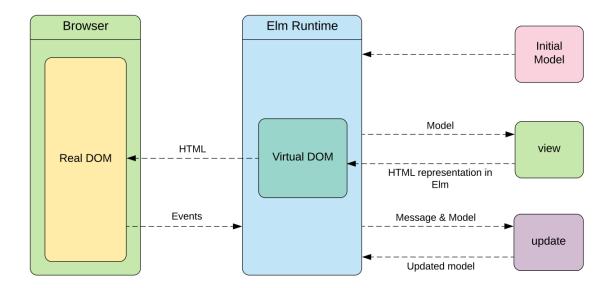

On initial inspection, the design decision of having a View function which repeatedly re-renders the Model every time there is some update appears inefficient. This would be the case if Elm (and other implementations of MVU) used the traditional process for rendering a web page/app. This traditional process for rendering HTML is shown in Figure 2.4. The HTML is parsed and a DOM (Document Object Model) is constructed; this is a tree representation of the HTML. Whenever the website/web app state changes, certain parts of the generated HTML change too. The DOM tree must be updated to reflect these changes, however this is often a slow process for large web apps with a large number of nodes in the DOM tree, resulting in the UI appearing sluggish. Elm combats this by using an intermediate Virtual DOM, a lightweight and optimised version of the main DOM tree on which operations are cheap. As shown in Figure 2.5, Elm exposes this virtual DOM to the programmer, who specifies how the state should be viewed in the View function. For each change of state, a new virtual DOM is constructed and compared to the previous virtual DOM. Through this, Elm can determine the exact change to the UI. Both the construction and comparison are fast due to the lightweight nature of the virtual DOM. Elm repeats this process for multiple changes to the UI, creating a batch of updates to be performed on the actual DOM tree at once. This method significantly reduces the per-update penalty for updating the DOM, allowing for efficient re-rendering of the program state. This improves the performance of the web app. Another advantage of this method is that the task of efficiently updating the DOM is abstracted away from the programmer, leaving them with only the task of specifying how their website or web app should look.

Figure 2.4: How browsers traditionally render HTML using a DOM [33]

#### React

React, as mentioned earlier, is a library for building user interfaces. In the Issie project, Elmish uses React for rendering the UI due to its efficient virtual DOM. Thus, the virtual DOM mentioned previously is actually the React Virtual DOM, which is a tree of React Elements. React Elements are simple objects, and are therefore cheap to create [34], meaning that operations on the React DOM are computationally inexpensive. The View function returns a React Element which shows the current state of the UI. React improves the performance of an application by only re-rendering elements when necessary. The React equivalent of the process mentioned previously where virtual DOMs are compared to find UI changes is called *Reconciliation* [34].

React also provides a further method for increasing performance: memoization [35]. Memoization is most useful when working with components whose state is partially dependent on computationally intensive calculation. Under traditional React, this value would be re-calculated on every render, even if it had not changed. This increases the amount of time each render takes. An example of this would be the result of the addition of two very large numbers (a + b), which is a very CPU

Figure 2.5: The Elm Architecture [33]

intensive task. Memoization combats this by caching the previous value of the computation and only performing the calculation whenever a or b changes. Issie already uses some memoization in its code for the Step Simulator: after a sheet is simulated for the first time the simulation is cached. If the sheet hasn't changed the next time a simulation is started, the cached simulation is used instead of building a new one, increasing performance.

#### Fulma

Fulma [36] is an F# library which provides a wrapper around Bulma [37], an open-source CSS framework which provides ready-to-use front-end components for building responsive web interfaces. Fulma brings these components to F# for use with Fable React. React components such as buttons, forms, and tables can easily be specified in the F# code using the functions provided by Fulma. Listing 2.1 shows the F# code for generating a table using Fulma, while Figure 2.6 shows the rendered table.

```

Table.table [ Table.IsBordered

Table.IsNarrow

Table. IsStriped ]

[ thead [ ]

[ tr [ ]

th [ ] [ str "Firstname" ]

th [ ] [ str "Surname" ]

th [ ] [ str "Birthday" ] ] ]

tbody [ ]

[ tr [ ]

[ td [ ] [ str "Maxime" ]

td [ ] [ str "Mangel" ]

td [ ] [ str "28/02/1992" ] ]

tr [ ClassName "is-selected" ]

[ td [ ] [ str "Jane" ]

[ ]

[ str "Doe" ]

[ ]

[ str "21/07/1987" ] ]

tr [

[ str "John" ]

[ td [ ]

[ str "Doe" ]

td [ ]

td [ ] [ str "11/07/1978" ] ] ]

```

Listing 2.1: Simple F# code for generating a table with Fulma [38]

| Firstname | Surname | Birthday   |  |  |  |  |

|-----------|---------|------------|--|--|--|--|

| Maxime    | Mangel  | 28/02/1992 |  |  |  |  |

| Jane      | Doe     | 21/07/1987 |  |  |  |  |

| John      | Doe     | 11/07/1978 |  |  |  |  |

Figure 2.6: Fulma Table Example

#### 2.4.4 Overview

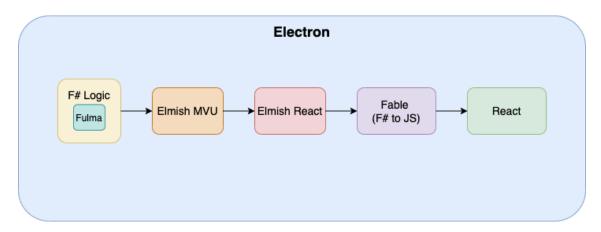

Figure 2.7: An Overview of Issie's Technology Stack

We can bring the above sections together to get an overview of Issie's Technology Stack, which is presented in Figure 2.7. The core logic of the Issie application is written in F#, with a structure which allows for adoption of the MVU architecture. Within the View function, using libraries like Fable.React and Fulma, HTML and React components can be specified. The Elmish library provides the MVU framework and methods for bringing together the Model data structure, View function, and Update function. A virtual DOM is necessary for an MVU application because it allows the application to frequently re-render its state after each update in an efficient manner. Due to its reliable and performant implementation of a virtual DOM, the React framework is used for Issie. The library Elmish.React handles the transition from the generic Elmish view to React, after which Fable compiles all of this F# code to JavaScript for React to render. All of this runs within Electron, allowing Issie to run as a desktop application despite having the technology stack of a web app.

#### 2.5 Issie's UI

#### 2.5.1 Overview and Evaluation

In line with the core principles that state all features implemented in Issie should be **Obvious** and **Intuitive**, Issie's UI aims to be consistent and straightforward. Consistency in the UI helps constantly prove a user's assumptions about the user interface right, creating a sense of control, familiarity, and reliability [39]. It also plays a crucial role in exposing all of the features of an application to the user – this is because features which are accessed in an inconsistent manner may be missed or incorrectly understood by end users. The intuitive guidance provided by a consistent and straightforward UI means that students using Issie spend less time learning how to use it compared to other similar applications; at it's launch most students were able to get started within five minutes [2]. With the limited amount of time in labs available, less time spent learning to use tools means more time spent on learning educational content.

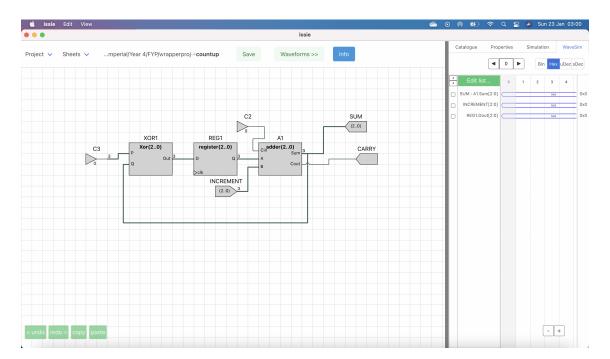

Since its original release, more features have been added to Issie, such as the Waveform Simulator, with the UI being updated to accommodate these features. At the time of writing, the latest release version of Issie is version 3.0.0, released on 16th April 2022. Images of Issie's UI can be found in Appendix A. On launch, Issie gives the user the option to create a new project or open an existing one. A project consists of one **main** sheet, and any number of sub-sheets, which define reusable custom components. Figure A.2 is an annotated screenshot of a sheet open in Issie. The UI can be split into the following sections, which are highlighted in different colours in Figure A.2.

Traditional Menu Bar (Highlighted Red): The traditional menu bar, consists of the "Edit" and "View" menus. It is not used to expose Issie's core features - instead, it is used to let the user do basic operations, such as zooming, copying and pasting etc. Many of these functions are duplicated through keyboard shortcuts or through the buttons in the bottom left of the sheet (undo, redo, copy, paste). The fact that Issie has two separate menus is a little strange, and it may be worth moving all functionality from the traditional menu bar to the top white menu bar. However, this is not an urgent cosmetic issue.

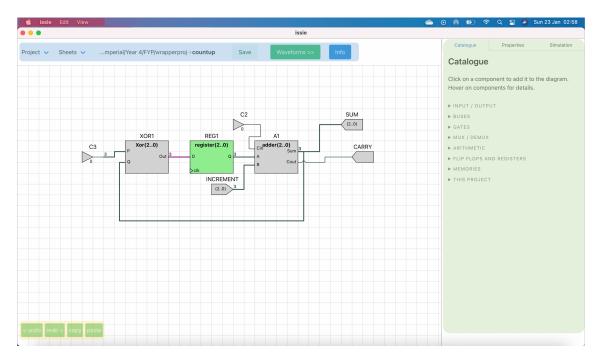

The Canvas: The canvas is the central focus of the application - it is where the schematic is designed. Components are dragged onto the canvas, with red-dashed lines appearing to show when a component is aligned with a grid line. Components and connections on the canvas can be interacted with in many ways, such as hovering, clicking to select, and dragging to move.

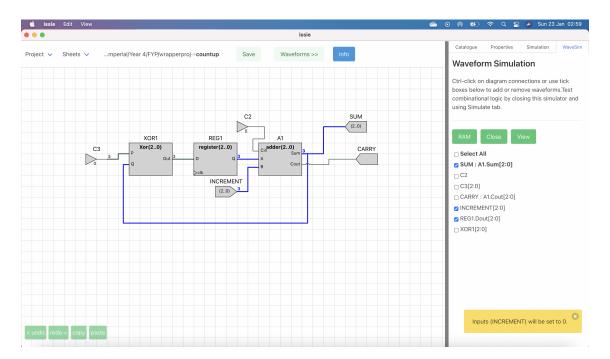

Right Tabs Panel (Highlighted Green): The panel on the right-hand side of the application provides the user with ways of (i) affecting the state of the canvas and (ii) gaining insight into the schematic itself. There are three tabs: the Catalogue, which lets users add new components to the canvas (users can hover on components for details); Properties, which lets users view and modify component properties like name and width, and Simulation, which opens the Step Simulator, giving users the option to start a simulation. Due to the Step Simulator requiring more display real-estate, the right panel widens when the Simulator tab is selected. When the Waveform Simulator is running, an additional fourth tab appears in this section – this makes the tab layout appear cramped.

Top Bar (Highlighted Blue): In the first release of Issie, the white menu bar located at the top of the application contained controls to, (i) save the current sheet, (ii) Switch to another sheet in the open project, and (iii) Open another or create a new project. The filepath of the current project and sheet are also displayed. All of these elements were consistent - with the focus on interacting with files. A slight grievance with the "Project" and "Sheets" dropdown menus is that they are not closed by clicking elsewhere in the application, only by clicking on the menu again. Since then, an "Info" button has been added featuring information about Issie and a short user guide. While this is not necessarily consistent with the other elements in its vicinity, the top bar enables the "Info" button to have maximum visibility, something which a student requiring information may appreciate. One very inconsistent part of the UI is how the Waveform simulator is accessed. While most actions which analyse the schematic (e.g. Step Simulator) are accessed via the Right Tabs panel, the Waveform simulator is opened through a button on the top bar. This causes the previously unseen "WaveSim" tab to spawn in the right panel, and the panel boundary becomes draggable. The user can select the waveforms to view (Figure A.3) and then view the waveforms (A.4. The Waveform simulator's behaviour is inconsistent with that of the Step simulator:

- Step Simulator displayed in a wider, fixed-width panel. Waveform Simulator displayed with panel starting at regular width, but the panel can be manually resized by dragging.

- The user can start a simulation in the Simulation tab, and still interact with other tabs.

This is not the case for the Waveform simulator, which locks the user in the WaveSim tab.

- Step Simulation started and ended with the same button, with a clear indication of how to end the simulation. There is no end/close button on the WaveSim tab when waveforms are being viewed. Instead, the user must press the "Edit List" button, which takes them back to the selection menu where there is a close button. This is very unintuitive.

Buttons on bottom-left (Highlighted Yellow): Undo, Redo, Copy, and Paste buttons. These are four common functions, and therefore it makes sense to have obvious and fast ways to access them. Useful to get started if the user is not familiar with keyboard shortcuts.

#### 2.5.2 Considerations when adding new features

As discussed in the previous section, Issie's UI at time of launch was very intuitive and straightforward. However, when there are fewer features it is easier to condense the interfaces for them into a well structured and streamlined UI. The inconsistencies of the Waveform Simulator tell a cautionary tale of how new features can introduce impurities into an application's GUI. This project aims to add a whole new way of visualising logic (truth tables) to Issie, and given the saturated nature of the current UI, some redesigning may be necessary to accommodate all features.

### 2.6 Combinational Logic Simulation in Issie

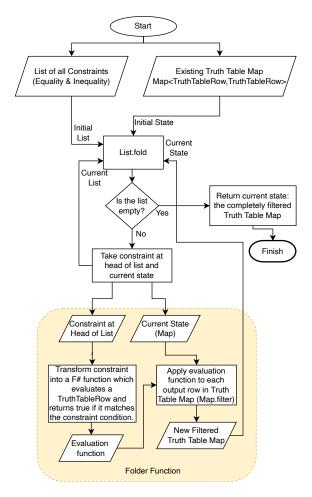

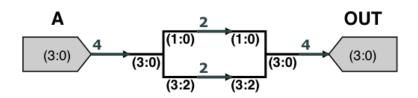

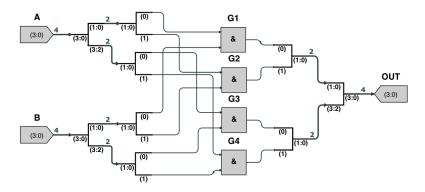

Currently in Issie, the users can gain an understanding of combinational logic by simulating it using the Step Simulator. Users provide values for each input to the logic, and can read the output almost instantly. This indicates high performance. Given that visualisation of combinational logic through truth tables is likely to require some form of combinational simulation, there is merit in exploring and understanding the implementation of the performant Step Simulator.